- �^�ԁE�d�l

�ꗗ���X�g - Q&A

�Z�p���- RTC���W���[����Q&A

- RTC���W���[���̋@�\

- �����U���q����RTC

���W���[���̃����b�g - RTC���W���[����

�����덷�i�����j - RTC���W���[����

��H�ڑ��� - RTC���W���[����

����d�� - RTC���W���[����

�o�b�N�A�b�v�d�� - RTC���W���[����

�d�������ؑ@�\ - ���x�⏞RTC���W���[��

�̉��x���� - RTC���W���[����

I2C�C���^�[�t�F�[�X - 32kHz�����U���q

�̉��x����

- �^�ԕʁ@

�v��� - �]���{�[�h

�@�]���c�[�� - �T�|�[�g

��� - RTC���W���[��

���p����

- �g�b�v

- �^�Ԗ���Q&A �y�ѐ��i�Z�p���

- RV-8263-C7 �̐ݒ� (�V���v���@�\�E�����d��RTC���W���[��)

![]()

�@RV-8263-C7�^RV-8263-C8 �̃��W�X�^�ݒ�E��H�v�ɂ���

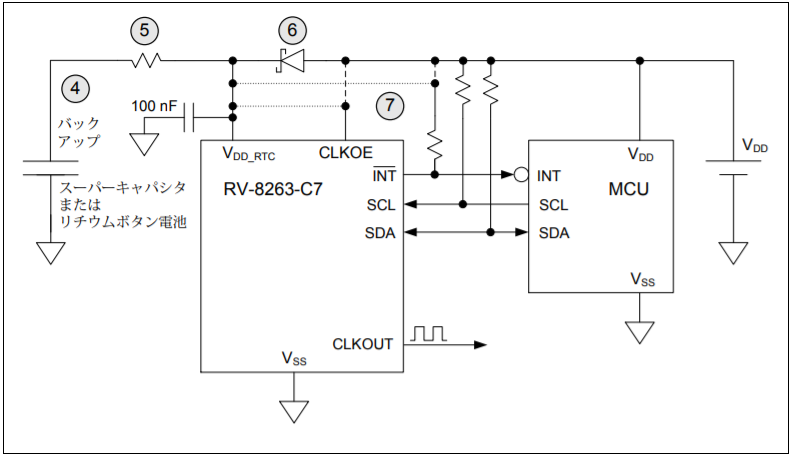

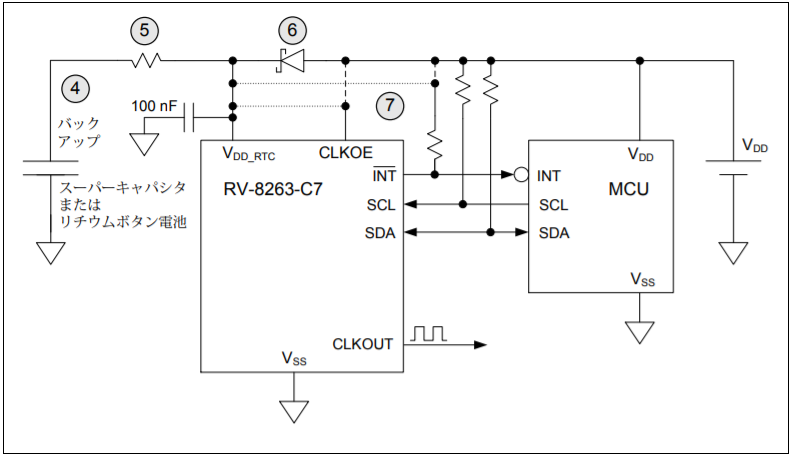

�@ ��H�ڑ���

�A RV-8263-C7�^RV-8263-C8 �̃��W�X�^�\��

�B �N�����Ƀp���[�I�����Z�b�g�Ń��W�X�^������������܂�

�C �����E�N�������̏����݁E�Ǎ��݁i04h�`0Ah)

�D �A���[���̐ݒ�

�E �J�E���g�_�E���E�^�C�}�̐ݒ�

�F �����X�V�����ݐM���̐ݒ�

�G �N���b�N�o�͂̐ݒ� �i32.768kHz�`1Hz�j

�H ���U��~���o�t���O �i�b���W�X�^�ւ̏����݂ŃN���A�j

�I �\�t�g�E�F�A���Z�b�g

�J �I�t�Z�b�g�ݒ�ɂ���

�@�@��H�ڑ���

�i�}�j���A��51�^61�y�[�W�j

�o�b�N�A�b�v�d���ڑ����܂߂���H�ڑ���ł��B

| �@�o�b�N�A�b�v�d�������`�E���ꎟ�d�r�̏ꍇ�͇E�̃_�C�I�[�h�ɉ����ćD�̕ی��R��VDD�̊Ԃɂ��_�C�I�[�h���K�v�ł��B�_�C�I�[�h�͘R��d���̏��Ȃ����̂����g�p������ (BAS-70�Ȃǁj�B�@�̃o�b�N�A�b�v�d�r���ϑw�Z���~�b�N�R���f���T�A�܂���2�d�w�R���f���T�A2���d�r�̏ꍇ�͏�}�̒ʂ�E�̃_�C�I�[�h�݂̂�ڑ����܂��B |

| �D��2�d�w�R���f���T�y�у��`�E���ꎟ�d�r�̕ی��R�ł��B�g�p����o�b�N�A�b�v�d���̎d�l�ɍ��킹�Ēl��ݒ肵�܂��B |

| �FVdd�[�q�̃p�X�R����0.01uF�`0.1uF�����g�p�������B |

|

�E �_�C�I�[�h�� Vf ��0.3V�ȉ��̂��̂ŁA���R��d���̏��Ȃ����̂����g�p�������B�@ |

| �GSDA / SCL / INT�[�q�͉�H��Vdd���C���փv���A�b�v�ڑ����܂��B |

→ RV-8263-C7 �̃o�b�N�A�b�v�d�r�t���]���{�[�h�̉�H�ڑ�������Q�Ɖ������B

�A�@RV-8263-C7 �^ RV-8263-C8�̃��W�X�^�\��

�B�@�N�����Ɏ����Ńp���[�I�����Z�b�g (POR)

�@�N�����Ɏ����Ńp���[�I�����Z�b�g�������背�W�X�^������������܂��B

�i�p���[�I�����Z�b�g�A�}�j���A��22�^61�y�[�W�j

���p���[�I�����Z�b�g��Ɂw�b���x�i04h�j���������ނ��Ƃ� OS�r�b�g(04h/7bit) ���N���A����܂��B

�@�@

�@�i���W�X�^�����l�ɂ��Ă� �}�j���A��21�^61�y�[�W ���Q�Ɖ������j

�C�@�����E�N�����̐ݒ�i04h�`0Ah )

�E���W�X�^�ڍׁF�}�j���A�� 14�`16�^61�y�[�W

�E�����f�[�^�̓ǂݍ��݁F�}�j���A��24�^61�y�[�W

�@�����E�N�����̃t�H�[�}�b�g�͈�ʓI��BCD�t�H�[�}�b�g�ł��B

�@�b�A���A���A���A�j���A���A�N�i����j���������݂܂��B

�@04h/bit:7 �́wOS�r�b�g�x�͗L���ȕb���i00�`59�j���������ނ��ƂŃN���A����܂��B

�������Ǐo���̃V�[�P���X�ɂ��ā�

�@�@ �����Ǐo���̍ۂ� ���U��~���o�� OS�r�b�g�i04h/7�r�b�g�j�̃t���O�������Ă����

�@�@�����ȕb��Ԃ���܂��i00�`59 �ȊO�̒l�j�B

�@�@���̏ꍇ�͓d���ቺ�ɂ������̐������U�킪��~���A������������Ȃ��Ȃ��Ă���\��������܂��B

�@�@→ ���U��~�����o���ꂽ�ꍇ�͎����̍Đݒ肪�K�v�ł��B

�D�@�A���[���̐ݒ�i0Bh�`0Fh )

�E���W�X�^�ڍׁF�}�j���A�� 17�`19�^61�y�[�W

�E����E�X�e�[�^�X�ڍׁF�}�j���A�� 12�^61�y�[�W

�E�A���[���@�\�F�}�j���A��26�^61�y�[�W

�E���荞�ݐM���o�͂̍\���F�}�j���A��25�^61�y�[�W

�� �A���[���́w�b�A���A���A�j���܂��͓��i1�`31���j�x�̒l��ݒ�\�ł��B

�E�@�J�Ԃ��J�E���g�_�E���^�C�}�̐ݒ�i0Bh�`0Dh �܂��� 1Bh�`1Dh )

�E���W�X�^�ڍׁi�^�C�}�J�E���g�ݒ�j�F�}�j���A�� 20�^74�y�[�W

�E����E�X�e�[�^�X�ڍׁF�}�j���A�� 12�^61�y�[�W

�E�J��Ԃ��J�E���g�_�E���^�C�}�@�\�F�}�j���A��27�`29�^61�y�[�W

�E���荞�ݐM���o�͂̍\���F�}�j���A��25�^61�y�[�W

�� �J�E���g�_�E���^�C�}�̃^�C�}�ݒ莞��

�@�@�^�C�}�ݒ莞�� �� �i�J�E���g�_�E���ݒ�l�j×�i1÷�^�C�}�N���b�N���g���j

�|�J�E���g�_�E���ݒ�l --- 0�`255�@�̊�

�|�^�C�}���N���b�N���g���@--- 4096Hz, 64Hz, 1Hz, 1/60Hz

∴ �ݒ�\�ȃ^�C�}�Ԋu --- �ŏ��l�F244.14μs�^�ő�l�F255���i4����15���j

�� �^�C�}�E���[�h�̑I���i�}�j���A��27/61�y�[�W�j

�@�|�C���^�[�o�����[�h (TI_TP�r�b�g��0�F�����l�j�E�E�ETF�t���O�������Ɋ��荞�ݐM���o��

�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�i�t���O�N���A�܂Ŋ��荞�ݐM���o�͂��p���j

�@�|�p���X���[�h (TI_TP�r�b�g��1 �j�E�E�E�J�E���g�_�E���I�����Ƃ�INT�[�q����p���X�M���o��

�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@ (�o�͎��ԁF122μs�`15.625ms�Ŏ����N���A����܂��j

�F�@�����X�V�i���b�܂��͖����j�����ݐM���̐ݒ�i 0Dh�܂��� 1Dh/Bit=5 )

�E����(2)���W�X�^�ڍׁF�}�j���A�� 12�^61�y�[�W

�E���� �܂��� 30�b�� �����ݐM���F�}�j���A��30�^74�y�[�W

�E���荞�ݐM���o�͂̍\���F�}�j���A��25�^61�y�[�W

�� �����X�V�i����X�V�j���荞�ݐM���́A30�b���܂��͖����̊����ݐM����ݒ�ł��܂��B

�G�@�N���b�N�o�͂̐ݒ�i0Bh�`0Dh �܂��� 1Bh�`1Dh )

�E����(2)���W�X�^�ڍׁF�}�j���A�� 12�^61�y�[�W

�E�N���b�N�o�͎��g���̐ݒ��̐ݒ�F�}�j���A�� 36�^61�y�[�W

���N���b�N�o�͂��s�v�ȏꍇ�́A����d����}���邽�߂� CLKOE�[�q�� Low �Ƃ��ăN���b�N�o�͂��I�t�ɂ��邱�Ƃ𐄏����܂��B

�@�i���W�X�^��FD�t�B�[���h�F01h�^Bit=2:0 �� �w111�x�Ƃ��ăN���b�N�o�̓I�t�ɂ��邱�Ƃ��o���܂��j

�@→ RV-8263-C7 �̏���d�� (CLKOUT �I���E�I�t�ł̈Ⴂ�j

�� FD�r�b�g�ݒ�l�ƃN���b�N�o�͎��g���̊W

( FD�t�B�[���h �F 01h�^Bit=2:0 )�B

| FD�ݒ�l | ���g�� |

| 000 | 32.768kHz�i�f�t�H���g�l�j |

| 001 | 16.384kHz |

| 010 | 8.192kHz |

| 011 | 4.096kHz |

| 100 | 2.048kHz |

| 101 | 1.024kHz |

| 110 | 1Hz |

| 111 | CLKOUT = LOW �i�o�͖����j |

�H�@���U��~���o�r�b�g (OS�r�b�g�j �i04h/bit:7)

�E�b���W�X�^�ڍׁF�}�j���A�� 14�^61�y�[�W

�wOS�r�b�g�x�͕b���W�X�^�ɗL���ȕb���i00�`59�j���������ނ��ƂŃN���A����܂��B

�i�ŏ��̎��������ݎ��� OS�r�b�g�̓N���A����܂��j

�� �����Ǐo���̍ۂ� ���U��~���o�� OS�r�b�g�i04h/7�r�b�g�j�̃t���O�������Ă����

�@�����ȕb��Ԃ���܂��i00�`59 �ȊO�̒l�j�B

�@�d���ቺ�ɂ������̐������U�킪��~�������Ƃ������Ă���A�����̍Đݒ肪�K�v�ł��B

�I�@SR�i�\�t�g�E�F�A���Z�b�g�j�r�b�g�ł̓��� �i 00h/bit:6, 4:3)

�E����E�X�e�[�^�X���W�X�^�ڍׁF�}�j���A�� 11�^61�y�[�W

�E�\�t�g�E�F�A���Z�b�g�@�\�F�}�j���A�� 22�^61�y�[�W

�p���[�I�����Z�b�g�Ɠ������Z�b�g�i���W�X�^�ݒ�̏������j���\�t�g�E�F�A�x�[�X�ōs���r�b�g�ł��B

�\�t�g�E�F�A�E���Z�b�g��, 00h�i ���䃌�W�X�^ (1) ) �� 6,4,3�r�b�g�� "1", ���̑��̃r�b�g�� "0"�Ƃ���,

�w01011000 (58h) �x�Ə������ނ��ƂŎ��{����܂��B

�J�@�I�t�Z�b�g�ݒ�ɂ��� �i 02h)

�E�I�t�Z�b�g���W�X�^�ڍׁF�}�j���A�� 13�^61�y�[�W

�E���g���I�t�Z�b�g�ɂ����F�}�j���A�� 31�`33�^61�y�[�W

�E���g���I�t�Z�b�g���荞�ݐM���ɂ����F�}�j���A�� 34�`35�^61�y�[�W

RV-8263-C7�^RV-8263-C8 �ɂ̓I�t�Z�b�g�@�\������A�����덷�̃I�t�Z�b�g����s�����Ƃ��o���܂��B

�������I�t�Z�b�g�����ʓI�ɍs�����߂ɂ́A1��Â��g���l�𑪒肵�ĕ�l�����肵�ĕ����K�v�����邽��

�ʎY���ɂ͌����I�ł͂Ȃ��A�ʏ�͂��̋@�\�͎g�p����܂���B

��萸�x�̗ǂ�������K�v�ȏꍇ�ɂ� RV-8803-C7, RV-3032-C7, RV-3028-C7 ����������܂��B

�I�t�Z�b�g��2���ԂɈ�x������{����m�[�}�����[�h�i����\�F4.34ppmTyp.)�ƁA4���Ɉ�����s����

�t�@�[�X�g���[�h�i����\�F4.069ppmTyp.)������܂��B�I�t�Z�b�g���{���Ɋ��荞�ݐM�����o�͂���

�w���g���I�t�Z�b�g���荞�݁x��ݒ�i2h/2bit : CIE�r�b�g�Őݒ�j���邱�Ƃ��o���܂��B

���֘A���

�E�^�ԕʂ�Q&A�E�v�T�|�[�g���

�� �v�E�J�����ɂ��s���ȓ_���������܂�����A���C�y�� ���Ђ̃T�|�[�g�����ւ��⍇���������B

- �g�b�v

- �^�Ԗ���Q&A �y�ѐ��i�Z�p���

- RV-8263-C7 �̐ݒ� (�V���v���@�\�E�����d��RTC���W���[��)