- �^�ԁE�d�l

�ꗗ���X�g - Q&A

�Z�p���- RTC���W���[����Q&A

- RTC���W���[���̋@�\

- �����U���q����RTC

���W���[���̃����b�g - RTC���W���[����

�����덷�i�����j - RTC���W���[����

��H�ڑ��� - RTC���W���[����

����d�� - RTC���W���[����

�o�b�N�A�b�v�d�� - RTC���W���[����

�d�������ؑ@�\ - ���x�⏞RTC���W���[��

�̉��x���� - RTC���W���[����

I2C�C���^�[�t�F�[�X - 32kHz�����U���q

�̉��x����

- �^�ԕʁ@

�v��� - �]���{�[�h

�@�]���c�[�� - �T�|�[�g

��� - RTC���W���[��

���p����

- �g�b�v

- �^�Ԗ���Q&A �y�ѐ��i�Z�p���

- RV-8803-C7 �̐ݒ� (�����x�E�����d��RTC���W���[��)

![]()

�@�@RV-8803-C7 �̃��W�X�^�ݒ�E��H�v�ɂ���

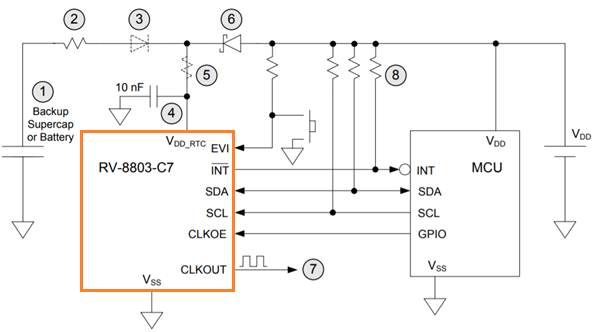

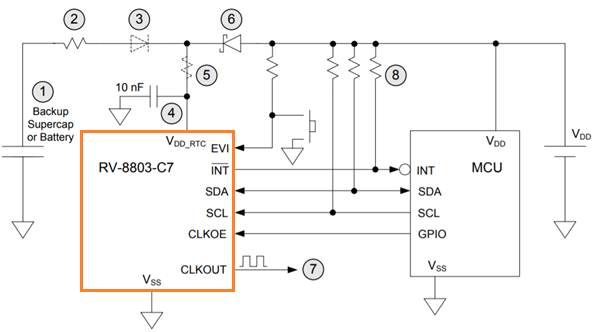

�@ ��H�ڑ���

�A RV-8803-C7�̃��W�X�^�\��

�B �N�����Ƀp���[�I�����Z�b�g�Ń��W�X�^������������܂�

�C �����E�N�������̏����݁E�Ǎ��݁i00h�`06h �܂���10h�`17h)

�D �A���[���̐ݒ�

�E �J�E���g�_�E���E�^�C�}�̐ݒ�

�F �����X�V�����ݐM���̐ݒ�

�G �N���b�N�o�͂̐ݒ� �i32.768kHz�`1Hz�j

�@(�N���b�N�o�͂̃I���E�I�t�� CLKOE�[�q�� Hi/Low�Ő��� �j

�H �O���C�x���g���́E�^�C���X�^���v�@�\�̐ݒ�

�I �d���ቺ���o�t���O �i�N�����ɃN���A�j

�J�I�t�Z�b�g�ݒ�

�K RESET�r�b�g�ł̓���

�LERST �r�b�g�ł̓���

�@�@��H�ڑ���

�i�}�j���A��64�^74�y�[�W�j

�o�b�N�A�b�v�d���ڑ����܂߂���H�ڑ���ł��B

| �@�����`�E���ꎟ�d�r�̏ꍇ�͇B�̃_�C�I�[�h���K�v�ł��B�_�C�I�[�h�͘R��d���̏��Ȃ����̂����g�p������ (BAS-70�Ȃǁj�B�@�̃o�b�N�A�b�v�d�r���ϑw�Z���~�b�N�R���f���T�A�܂���2�d�w�R���f���T�A2���d�r�̏ꍇ�͇B�̃_�C�I�[�h�͎g�p���܂���B |

| �A��2�d�w�R���f���T�y�у��`�E���ꎟ�d�r�̕ی��R�ł��B�g�p����o�b�N�A�b�v�d���̎d�l�ɍ��킹�Ēl��ݒ肵�܂��B |

| �CVdd�[�q�̃p�X�R����0.01uF�`0.1uF�����g�p�������B |

| �DVdd�[�q�ւ̃V���[�Y��R�́A�}�j���A��62�^74�y�[�W �ɋL�ڂ̓d���o�b�N�A�b�v�̐ؑ֎���Vdd�[�q�̓d��������^�����̃X���[���[�g���K��l���Ă��܂��ꍇ�ɒ����̂��ߕK�v�ɂȂ�܂��B |

| �E �_�C�I�[�h�� Vf ��0.3V�ȉ��̂��̂ŁA���R��d���̏��Ȃ����̂����g�p�������B�@ �� �����i�ԁFBAS-70�V���[�Y (Diodes, Vishay ���j |

| �GSDA / SCL / INT�[�q�͉�H��Vdd���C���փv���A�b�v�ڑ����ĉ������B |

���wEVI�[�q�x���g�p���Ȃ��ꍇ�� GND�ڑ��Ƃ��t���[�g�ɂ͂��Ȃ��ʼn������B

�@�i�t���[�g��Ԃ̂܂܂ɂ���Ɛ�μA�Ȃ�����d���d�����啝�ɑ����Ă��܂��ꍇ������܂��j

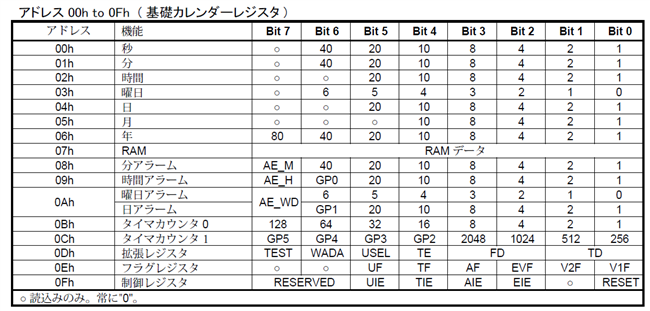

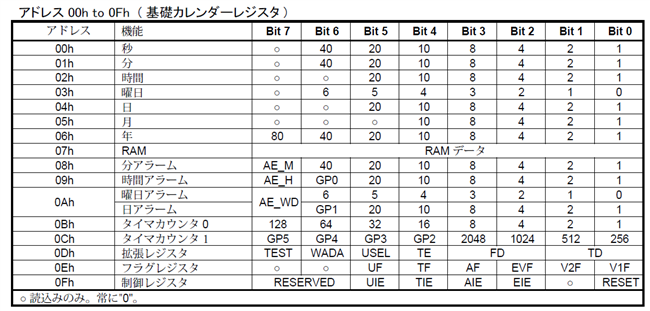

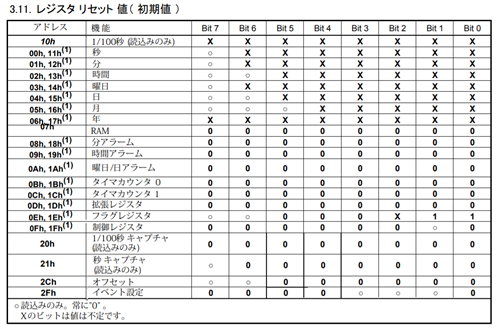

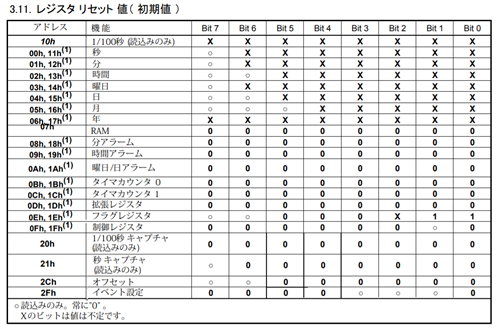

�A�@RV-8803-C7�̃��W�X�^�\��

�i�}�j���A��11�`12�^74�y�[�W�j

�B�@�N�����Ƀp���[�I�����Z�b�g (POR)

�@�N�����Ɏ����Ńp���[�I�����Z�b�g�������背�W�X�^������������܂��B

�i�p���[�I�����Z�b�g�A�}�j���A��26�^74�y�[�W�j

�� �p���[�I�����Z�b�g��� V2F�t���O�AV1F�t���O (1Eh/�r�b�g�F1�y��0�j �������Ă����Ԃł��̂�

f/w �̐ݒ�Ńp���[�I�����Z�b�g����ɃN���A���ĉ������B

�@�@

�@�i���W�X�^�����l�ɂ��Ă� �}�j���A��25�^74�y�[�W ���Q�Ɖ������j

�C�@�����E�N�����̐ݒ�i00h�`06h �܂��� 11h�`17h )

�E���W�X�^�ڍׁF�}�j���A�� 13�`15�^74�y�[�W

�E�����f�[�^�̓ǂݍ��݁F�}�j���A��42�^74�y�[�W

�@�����E�N�����̃t�H�[�}�b�g�͈�ʓI��BCD�t�H�[�}�b�g�ł��B

�@�b�A���A���A�j���A���A���A�N�i����j���������݂܂��B

�@1/100�b�J�E���^���W�X�^ (10h)�̒l�͓ǂݍ��݂݂̂ł��B

�������Ǐo���̃V�[�P���X�ɂ��ā�

�@(1) �����Ǐo���̍ۂɂ� �d���ቺ���o�t���b�O�r�b�g(V1F�r�b�g�^V2F�r�b�g)

�@�@��Ǎ���Œl�̗L�������m�F���܂��B

�@�@�@→ �d���ቺ�����o���ꂽ�ꍇ�͎����̍Đݒ肪�K�v�ł��B

�@(2)�w���x�̏I���̒l�̓ǂݍ��ݎ��̒���

�w�b���W�X�^�x�̓ǂݎ��l�� "59�b"�������ꍇ�ɂ́A�ēx�J��Ԃ��ĕb���W�X�^��ǂݍ���Ŕ�r���邱�Ƃ𐄏����܂��B

�@1. �����E�J�����_�[����ǂݍ��݂܂��B

�@2. �b��� "59�b"�������ꍇ�ɂ͍ēx�J��Ԃ������E�J�����_�[����ǂݍ��݂܂��B

�@3. �ォ��ǂݍ������̕b���"59�b"�������ꍇ��, �ŏ��̓Ǎ��ݒl�͐������������ł��B

�@4. �ォ��ǂݍ��l�����̕b��i��ł����ꍇ��, �����E�J�����_�[��ŏ��̓Ǎ��݂̊ԂŃC���N�������g���Ă��܂��Đ������Ȃ��\��������܂��B

�@�@���̏ꍇ�ɂ͌ォ��ǂݍ������E�J�����_�[��ԈႢ�̖����������������ł��B

�@�@→ �}�j���A�� 42/74�y�[�W �����Q�Ɖ������B

�D�@�A���[���̐ݒ�i08h�`0Ah �܂��� 18h�`1Ah )

�E���W�X�^�ڍׁF�}�j���A�� 16�`17�^74�y�[�W

�E�t���O���W�X�^�ڍׁF�}�j���A�� 20�^74�y�[�W

�E���䃌�W�X�^�ڍׁF�}�j���A�� 21�^74�y�[�W

�E�A���[�����荞�ݐM���@�\�F�}�j���A��34�`35�^74�y�[�W

�� �A���[���́w���A���A�j���܂��͓��i1�`31���j�x�Őݒ�ł��܂��B

�E�@�J�Ԃ��J�E���g�_�E���^�C�}�̐ݒ�i0Bh�`0Dh �܂��� 1Bh�`1Dh )

�E���W�X�^�ڍׁi�^�C�}�J�E���g�ݒ�j�F�}�j���A�� 18�^74�y�[�W

�E�g�����W�X�^�ڍׁi�^�C�}���g���ݒ�j�F�}�j���A�� 19�^74�y�[�W

�E�t���O���W�X�^�ڍׁF�}�j���A�� 20�^74�y�[�W

�E���䃌�W�X�^�ڍׁF�}�j���A�� 21�^74�y�[�W

�E�J��Ԃ��J�E���g�_�E���^�C�}���荞�ݐM���@�\�F�}�j���A��29�`31�^74�y�[�W

�� �J�E���g�_�E���^�C�}�̃^�C�}�ݒ莞�Ԃ͈ȉ��ɂȂ�܂��B

�^�C�}�ݒ莞�� �� �i�J�E���g�_�E���ݒ�l�j×�i1÷�^�C�}�N���b�N���g���j

�|�J�E���^�ݒ�l --- 0�`4095�@�̊�

�|�^�C�}���N���b�N���g���@--- 4096Hz, 64Hz, 1Hz, 1/60Hz

∴ �ݒ�\�ȃ^�C�}�Ԋu --- �ŏ��l�F244.14μs�^�ő�l�F4095��

�F�@�����X�V�i���b�܂��͖����j�����ݐM���̐ݒ�i 0Dh�܂��� 1Dh/Bit=5 )

�E�g�����W�X�^�ڍׁF�}�j���A�� 19�^74�y�[�W

�E�t���O���W�X�^�ڍׁF�}�j���A�� 20�^74�y�[�W

�E���䃌�W�X�^�ڍׁF�}�j���A�� 21�^74�y�[�W

�E�����X�V���荞�ݐM���@�\�F�}�j���A��32�`33�^74�y�[�W

�� �����X�V�i����X�V�j���荞�ݐM���́A���b�܂��͖����̊����ݐM����ݒ�ł��܂��B

�G�@�N���b�N�o�͂̐ݒ�i0Bh�`0Dh �܂��� 1Bh�`1Dh )

�E�g�����W�X�^�ڍׁF�}�j���A�� 19�^74�y�[�W

�E�N���b�N�o�͎��g���̐ݒ��̐ݒ�F�}�j���A�� 40�^74�y�[�W

���N���b�N�o�͂��s�v�ȏꍇ�́A����d����}���邽�߂� CLKOE�[�q�� Low �Ƃ��ăN���b�N�o�͂��I�t�ɂ��邱�Ƃ𐄏����܂��B

�@→ RV-8803-C7 �̏���d�� (CLKOUT �I���E�I�t�ł̈Ⴂ�j

�� FD�r�b�g�ݒ�l�ƃN���b�N�o�͎��g���̊W

( FD�r�b�g �F 0Dh�܂���1Dh�^Bit=3:2 )�B

| FD�ݒ�l | ���g�� |

| 00 | 32.768kHz�i�f�t�H���g�l�j |

| 01 | 1024Hz |

| 10 | 1Hz |

| 11 | 32.768kHz |

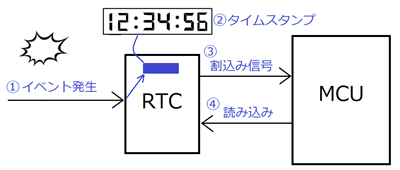

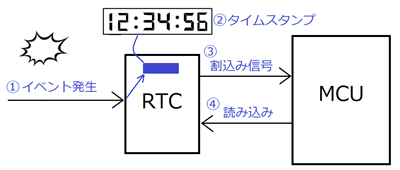

�H�@�O���C�x���g���͂̐ݒ�i2Fh )�@�^�C���X�^���v�@�\

�E�t���O���W�X�^�ڍׁF�}�j���A�� 20�^74�y�[�W

�E�O���C�x���g���͐ݒ背�W�X�^�F�}�j���A�� 24�^74�y�[�W

�E�O���C�x���g�����F�}�j���A�� 36�`38�^74�y�[�W

EVI�[�q�M�����͂��ꂽ���荞�ݐM�������y�є��������̃^�C���X�^���v����邱�Ƃ��o���܂��B

�C�x���g�������� �w1/100�b�J�E���^�x�y�сw�b�J�E���^�x�̒l�� �w20h���W�X�^ (1/100�b)�x�w21h���W�X�^(�b)�x�֏������܂�܂��B

�܂��C�x���g�����i���o�j���Ɂw�O���C�x���g���荞�ݐM���x���o�͂�����ݒ肪�o���܂��B

����ɂ��C�x���g�������}�C�R���ɒm�点��RTC�����̃^�C���X�^���v��ǂݍ��܂��邱�Ƃ��o���܂��B

�@�O���C�x���g�����������AEVI�[�q�ɊO���M�������͂����

�ARTC�����̃������i���W�X�^�j�Ƀ^�C���X�^���v���L�^����܂��B

�B������INT�[�q����MCU�Ɋ����ݐM���𑗂�܂��B

�i�O���C�x���g���͊��荞�ݐM���o�͂�L���ɐݒ肵�Ă����܂��j

�C���荞�ݐM�����g���K�Ƃ���MCU ���烊�A���^�C���N���b�N�����̃^�C���X�^���v��ǂݍ��݂܂��B

�I�@�d���ቺ���o�t���O �i0Eh�܂��� 1Eh)

�E�t���O���W�X�^�ڍׁF�}�j���A�� 20�^74�y�[�W

�E V2F�r�b�g�@(0Eh�܂���1Eh�^ Bit=1 )

�d���ቺ�ɂ�莞�v���̐��x�������ɂȂ����\��������ꍇ�Ƀt���O�������܂��B

���o臒l��1.1�`1.3V (1.2V Typ.)�B�@

�EV1F�r�b�g (0Eh�܂���1Eh�^ Bit=0)

�d���ቺ�ɂ�艷�x�⏞���삪�������s���Ȃ��Ȃ����\��������ꍇ�Ƀt���O�������܂��B

���o臒l��1.1�`1.3V (1.2V Typ.)�B

�� �����ǂݍ��ݑO�ɂ����̃t���O���m�F���A�t���O�������Ă���ꍇ�͎����������ɂȂ��Ă��邽��

�@�ēx�̎����ݒ肪�K�v�ł��B

�� �N�����ɂ͂����̃t���O�������Ă���̂ŁA�N������̃V�[�P���X�ŃN���A���Ă����K�v������܂��B

�J�@���g���I�t�Z�b�g�ݒ� �i2Ch)

�E�ݒ背�W�X�^�ڍׁF�}�j���A�� 24�^74�y�[�W

�E�I�t�Z�b�g�ݒ��F�}�j���A�� 45�^74�y�[�W

1Hz�N���b�N�̕����I�t�Z�b�g�ݒ肷�郌�W�X�^�ł��B

�� �I�t�Z�b�g�̓��[�J�[�o���ɐݒ肳��Ă���A�ʎY���ɌʂɃI�t�Z�b�g�ݒ肷��K�v�͂���܂����B

�@�܂��̓��t���[�ł̕ϓ��̕��ϓI�Ȓl�����z�����l�i-0.5�`-1.0ppm���x�Ȃǁj�����炩����f/w�ɐݒ肵�܂��B

�E�I�t�Z�b�g�r�b�g�i2Ch�^Bit=5:0�j�̒l�ƃI�t�Z�b�g�l

��0.238ppm�X�e�b�v�ׂ̍����ݒ肪�\�ł��B

| �I�t�Z�b�g�ݒ�l | �I�t�Z�b�g�l |

| 0x04 | +0.952ppm |

| 0x03 | +0.714ppm |

| 0x02 | +0.477ppm |

| 0x01 | +0.238ppm |

| 0x00 | 0.000ppm |

| 0x3F | -0.238ppm |

| 0x3E | -0.477ppm |

| 0x3D | -0.714ppm |

| 0x3C | -0.952ppm |

| 0x3B | -1.190ppm |

| 0x3A | -1.428ppm |

| 0x39 | -1.666ppm |

| 0x38 | -1.904ppm |

| 0x37 | -2.142ppm |

| 0x36 | -2.380ppm |

| 0x35 | -2.618ppm |

�K�@RESET �i���Z�b�g�j�r�b�g�ł̓��� �i 0Fh/Bit:0 �܂��� 1Fh/Bit:0)

�E���䃌�W�X�^�ڍׁF�}�j���A�� 21�^74�y�[�W

�ERESET �r�b�g�̋@�\�F�}�j���A�� 43�^74�y�[�W

�\�t�g�E�F�A�x�[�X�Ŏ�����������邽�߂̐ݒ�r�b�g�ł��B

RESET �r�b�g��"1"�Ƃ��ă��Z�b�g����������Ɠ����̎��v�̓��Z�b�g�������[�X�����܂Œ�~���܂��B

���� 1/100�b�J�E���^��"00"�ɃZ�b�g����܂��B

�ēx�A�����E�N����������܂�� RESET�r�b�g�������[�X�i"0"�ɏ����݁j����Ǝ��v������ĊJ���܂��B

1/100�b�J�E���^��"00"���瓮����J�n���܂��B

�L�@ERST�i�C�x���g���Z�b�g�j�r�b�g�ł̓��� �i 2Fh/Bit=0 )

�E�C�x���g�ݒ背�W�X�^�ڍׁF�}�j���A�� 24�^74�y�[�W

�E�C�x���g���Z�b�g (ERST) �@�\�F�}�j���A�� 43�^74�y�[�W

ERST�r�b�g�� "1"�ɐݒ肳���ƊO���C�x���g���͎��̃L���v�`���i�^�C���X�^���v�j�A

�y��1/100�b�J�E���^��"0" �Ƀ��Z�b�g����܂��B

ERST�i�C�x���g���Z�b�g�j �ł͊O���M�����͂���Ƃ��� 1/100�b�J�E���^��"00"�Ƀ��Z�b�g����邽�߁A

��q�� RESET�i�\�t�g�E�F�A���Z�b�g�j�ɔ�ׂă\�t�g�E�F�A�����̒x���덷�̖������x�̍���1/100�J�E���^���Z�b�g���s���܂��B

���֘A���

�E�^�ԕʂ�Q&A�E�v�T�|�[�g���

�ERV-8803-C7��p�����s�����o�E�h�~�^�^�C���X�^���v�̎擾

�� �v�E�J�����ɂ��s���ȓ_���������܂�����A���C�y�� ���Ђ̃T�|�[�g�����ւ��⍇���������B

- �g�b�v

- �^�Ԗ���Q&A �y�ѐ��i�Z�p���

- RV-8803-C7 �̐ݒ� (�����x�E�����d��RTC���W���[��)